Zdarzenie w systemie komputerowym wymagające przerwania wykonania bieżącego strumienia instrukcji i przekazania sterowania do systemu operacyjnego

Podział sytuacji wyjątkowych

Przerwa

-

Powstają poza procesorem

-

za wyjątkiem asynchronicznego przerwania programowego

-

Asynchroniczne względem wykonywanego strumienia instrukcji

-

ich wystąpienie nie jest bezpośrednim wynikiem wykonania konkretnej instrukcji

-

Służą do sygnalizacji zdarzeń istotnych dla systemu operacyjnego

-

zmiana kontekstu rządzeń zewnętrznych, np.

-

wciśnięcie klawisza na klawiaturze, przesunięcie myszy

-

nadejście pakietu z sieci lokalnej

-

zakończenie transmisji danych do/z pamięci masowej

-

upłynięcie określonego odcinka czasu

-

timer systemowy służący do periodycznego przełączania procesów w systemie wieloprocesowym

-

"budzenie" procesu o określonym czasie

Pułapki

-

Generowane przez procesor

-

Powodowane przez konkretną instrukcję, na końcu wykonania instrukcji

-

ściśle synchroniczne względem instrukcji

-

Rodzaje:

-

wywołanie usługi systemu operacyjnego przez program użytkowy (często niezbyt fortunnie nazywana "przerwaniem programowym")

-

MIPS - instrukcja SYSCALL

-

sygnalizacja błędów wykonania wykrytych przez program użytkowy do systemu operacyjnego

-

MIPS - instrukcje ADD, SUB - w przypadku wystawienia nadmiaru generują pułapkę

-

x86 - instrukcje dzielenia DIV, IDIV, AAM generują pułapkę przy nadmiarze

-

pułapka śledzenia (tracę trap) - wygenerowana po wykonaniu dowolnej instrukcji przy ustawionym trybie śledzenia

Błędy

-

Generowane na ogół przez procesor

-

zarówno przez jednostkę wykonawczą jak i przez jednostkę zarządzania pamięcią

-

wyjątek - błąd transmisji - generowany poza procesorem

-

Wynikają z wykonywanych instrukcji, ale nie zawsze w sposób jednoznaczny

-

Służą do sygnalizacji błędnych i niedozwolonych zachowań oprogramowania i sprzętu

-

próba wykonania niezdefiniowanej instrukcji

-

błąd wyrównania przy dostępie do pamięci

-

naruszenie zasad ochrony

-

Wykorzystywane do implementacji systemu pamięci wirtualnej

Obsługa wyjątków

-

Każdy wyjątek musi być obsłużony

-

Istnieją dwa pojęcia obsługi:

-

na poziomie oprogramowania - reakcja programowa systemu operacyjnego na zdarzenie

-

np. przesłanie kolejnej porcji danych do urządzenia zgłaszającego gotowość

-

przełączenie procesów przy przerwaniu timera

-

na poziomie procesora - zespół czynności, których efektem jest zaniechanie wykonywania bieżącego strumienia instrukcji i rozpoczęcie wykonanie programowej procedury systemu operacyjnego

-

obsługa wyjątku przez system operacyjny rozpoczyna się z chwilą zakończenia obsługi wyjątku przez procesor

Obsługa wyjątku przez procesor - fazy

-

Rozpoznanie i identyfikacja źródła wyjątku

-

Przerwanie wykonania strumienia instrukcji i zapamiętanie bieżącego kontekstu procesora

-

Załadowanie nowego kontekstu procesora i rozpoczęcie wykonywania nowego strumienia instrukcji - procedury systemowej zapewniającej programową reakcję systemu na wyjątek

Identyfikacja wyjątku

-

Jeśli wyjątek powstał w procesorze (pułapka, błąd) - procesor zna dokładną jego przyczynę

-

identyfikacja jest zbędna

-

Przerwania:

-

w zależności od budowy systemu przerwań identyfikacja może być przerowadzona później przez oprogramowanie albo w chwili wykrycia wyjątku - przez sprzęt procesora

-

identyfikacja przez procesor wymaga przeprowadzenia zapytania, w postaci specjalnego cyklu transmisji - cyklu identyfikacji przerwania

-

w odpowiedzi na cykl identyfikacji procesor otrzymuje z zewnątrz identyfikator przerwania w postaci liczby o długości od 4 do 9 bitów

-

x86 - 8 bitów

-

M88k - 9 bitów

-

mikrokontrolery 8- i 16-bitowe - 4..8 bitów

-

identyfikator jest generowany przez układ arbitrażu przerwań

Zapamiętanie kontekstu

-

Co zapamiętywać?

-

informacje o stanie procesora, które zostaną samoczynnie zmodyfikowane przez procesor w czasie obsługi wyjątku

-

zawsze PC i rejestr stanu z informacjami systemowymi

-

rejestry uniwersalne jest zbędne, bo może to zrobić oprogramowanie

-

informacje niezbędne do rozpoznania dokładnej przyczyny wyjątku, a które mogą zostać zamazane w trakcie wykonania programu

-

informacje o odwołaniu do pamięci przy błędzie dostępu

-

Gdzie zapamiętywać?

-

w miejscu naturalnym dla danej architektury

-

CISC - na stosie

-

RISC - zwykle w rejestrach

-

Po co?

-

powrót po obsłudze

-

komunikat diagnostyczny w przypadku usunięcia błędnego procesu

Składanie kontekstu - licznik instrukcji

-

Zapamiętywany w celu powrotu do przerwanego programu lub wyświetlenia komunikatu o błędzie

-

Podczas wyjątku wartość nextPC nie zawsze jest dostępna

-

błędy przerywają wykonanie instrukcji - instrukcja niedokończona

-

Zapamiętywana wartość:

-

nextPC - wskazuje na następną instrukcję po tej. w czasie której wykryto wyjątek

-

przerwania

-

pułapki wywołania systemu i śledzenia

-

currentPC - wskazuje na bieżącą instrukcję

-

pułapki sygnalizujące bład wykonania (potrzebna identyfikacja miejsca błędu)

-

błędy - wykonanie instrukcji było niemożliwe - jeśli nastąpi powrót, to ponownie do tej samej instrukcji

-

Niektóre procesory RISC zapamiętują nextPC+4 lub nextPC+8

Zmiany kontekstu systemowego w czasie obsługi wyjątku

-

Obsługa wyjątku powoduje zawsze przejście w tryb systemowy

-

podczas wystąpienia wyjątku procesor mógł być w trybie systemowym lub użytkownika

-

należy zapamiętać poziom zaufania z chwili wystąpienia wyjątku

-

Przy obsłudze wyjątku jest wyłączany tryb śledzenia

-

bit śledzenia znajduje się w rejestrze stanu procesora

-

Przy obsłudze przerwania procesor zmienia poziom wrażliwości na przerwanie

-

należy zapamiętać poziom wrażliwości (tzw. maskę przerwań) z chwili wystąpienia przerwania

-

Wszystkie powyższe informacje znajdują się zwykle w systemowym rejestrze stanu procesora

-

podczas obsługi wyjątków należy zapamiętać systemowy rejestr stanu

Składowanie PC i rejestru stanu

-

W procesorach RISC:

-

zawartość PC i SR kopiowana do rejestrów cieni

-

alternatywa - przełączenie banku rejestrów (w procesorach z oddzielnymi rejestrami do obsługi wyjątków)

-

W procesorach CISC:

-

PC i SR zapamiętywane na stosie

-

program użytkowy nie daje gwarancji integralności stosu

-

wartość SP może być nieważna

-

kontekst jest składowany na stosie systemowym

-

każdemu poziomowi zaufania odpowiada oddzielny stos

-

kolejność czynności:

-

utworzenie tymczasowej kopii rejestru stanu

-

przełączenie w tryb systemowy (modyfikacja rejestru stanu)

-

zapamiętanie tymczasowej kopii rejestru stanu na stosie systemowym

Przełączanie stosów w procesorach CISC

-

Każdemu poziomowi zaufania odpowiada oddzielny stos

-

Przy zmianie poziomu zaufania następuje przełączenie stosów

-

można to zrealizować na dwa sposoby

-

oddzielny rejestr wskaźnika stosu dla każdego poziomu zaufania (np. M68k)

-

przeładowanie wskaźnika stosu przez procesor przy użyciu wartości zapisanych w pamięci (np. x86)

-

Na danym poziomie zaufania oprogramowanie może mieć dostęp do własnego wskaźnika stosu i wskaźników stosów poziomów mniej zaufanych

-

oprogramowanie systemowe może inicjować wskaźnik stosu użytkownika

-

instrukcje dostępu do alternatywnych wskaźników stosu są dozwolone tylko w trybie systemowym

Informacje potrzebne do obsługi błędu

-

Błąd różni się od innych wyjątków tym, że uniemożliwia wykonanie bieżącej instrukcji

-

nextPC jest niedostępny lub nieważny - zapamiętuje się currPC

-

Błąd sygnalizowany przez MMU może wynikać z pobrania instrukcji lub z dostępu do danych

-

do identyfikacji przyczyny błędu potrzebna jest informacja o adresie i rodzaju odwołania, które spowodowało błąd

-

sam adres instrukcji nie umożliwia jednoznacznej identyfikacji przyczyny błędu

-

Niektóre architektury umożliwiają wykonywa nie odwołań w trybie systemowym z poziomem zaufania użytkownika

-

ułatwia to ochronę systemu

-

poziom zaufania odwołania musi być w takim przypadku zapamiętany niezależnie od poziomu zaufania procesora

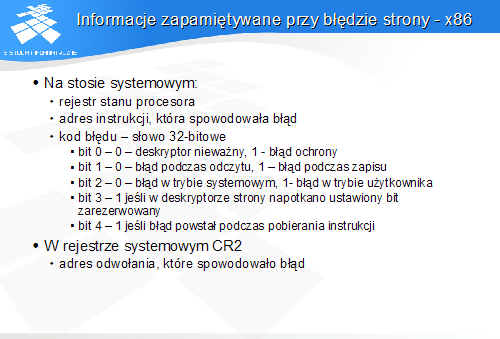

Informacje zapamiętywane przy błędzie strony - x86

-

Na stosie systemowym:

-

rejestr stanu procesora

-

adres instrukcji, która spowodowała błąd

-

kod błędu - słowo 32-bitowe

-

bit 0 - 0 - deskryptor nieważny, 1 - błąd ochrony

-

bit 1 - 0 - błąd podczas odczytu, 1 - błąd podczas zapisu

-

bit 2 - 0 - błąd w trybie systemowym. 1 - błąd w trybie użytkownika

-

bit 3 - 1 jeśli w deskryptorze strony napotkano ustawiony bit zarezerwowany

-

bit 4 - 1 jeśli błąd powstał podczas pobierania instrukcji

-

W rejestrze systemowym CR2

-

adres odwołania, które spowodowało błąd

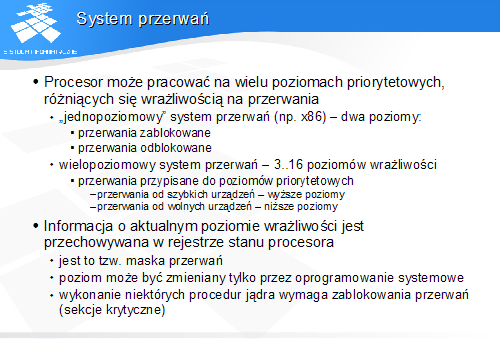

System przerwań

-

Procesor może pracować na wielu poziomach priorytetowych, różniących się wrażliwością na przerwania

-

"jednopoziomowy" system przerwań (np. x86) - dwa poziomy

-

przerwania zablokowane

-

przerwania odblokowane

-

wielopoziomowy system przerwań - 3..16 poziomów wrażliwości

-

przerwania przypisane do poziomów priorytetowych

-

przerwania od szybkich urządzeń - wyższe poziomy

-

przerwania od wolnych urządzeń - niższe poziomy

-

Informacja o aktualnym poziomie wrażliwości jest przechowywana w rejestrze stanu procesora

-

jest to tzw. maska przerwań

-

poziom może być zmieniany tylko przez oprogramowanie systemowe

-

wykonanie niektórych procedur jądra wymaga zablokowania przerwań (sekcje krytyczne)

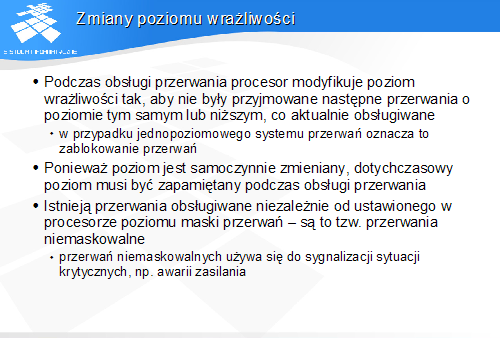

Zmiany poziomu wrażliwości

-

Podczas obsługi przerwania procesor modyfikuje poziom wrażliwości tak, aby nie były przyjmowane następne przerwania o poziomie tym samym lub niższym, co aktualnie obsługiwane

-

w przypadku jednopoziomowego systemu przerwań oznacza to zablokowanie przerwań

-

Ponieważ poziom jest samoczynnie zmieniany, dotychczasowy poziom musi być zapamiętany podczas obsługi przerwania

-

Istnieją przerwania obsługiwane niezależnie od ustawionego w procesorze poziomu maski przerwań - są to tzw. przerwania niemaskowalne

-

przerwań niemaskowalnych używa się do sygnalizacji sytuacji krytycznych, np. awarii zasilania

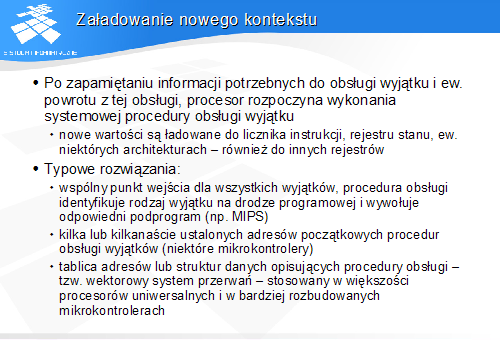

Załadowanie nowego kontekstu

-

Po zapamiętaniu informacji potrzebnych do obsługi wyjątku i ew. powrotu z tej obsługi, procesor rozpoczyna wykonania systemowej procedury obsługi wyjątku

-

nowe wartości są ładowane do licznika instrukcji, rejestru stanu. ew. niektórych architekturach - również do innych rejestrów

-

Typowe rozwiązania:

-

wspólny punkt wejścia dla wszystkich wyjątków, procedura obsługi identyfikuje rodzaj wyjątku na drodze programowej i wywołuje odpowiedni podprogram (np. MIPS)

-

kilka lub kilkanaście ustalonych adresów początkowych procedur obsługi wyjątków (niektóre mikrokontrolery)

-

tablica adresów lub struktur danych opisujących procedury obsługi -tzw. wektorowy system przerwań - stosowany w większości procesorów uniwersalnych i w bardziej rozbudowanych mikrokontrolerach

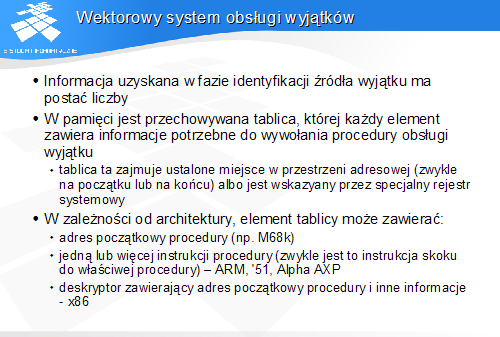

Wektorowy system obsługi wyjątków

-

Informacja uzyskana w fazie identyfikacji źródła wyjątku ma postać liczby

-

W pamięci jest przechowywana tablica, której każdy element zawiera informacje potrzebne do wywołania procedury obsługi wyjątku

-

tablica ta zajmuje ustalone miejsce w przestrzeni adresowej (zwykle na początku lub na końcu) albo jest wskazyany przez specjalny rejestr systemowy

-

W zależności od architektury, element tablicy może zawierać:

-

adres początkowy procedury (np. M68k)

-

jedną lub więcej instrukcji procedury (zwykle jest to instrukcja skoku do właściwej procedury) - ARM, '51, Alpha AXP

-

deskryptor zawierający adres początkowy procedury i inne informacje - x86

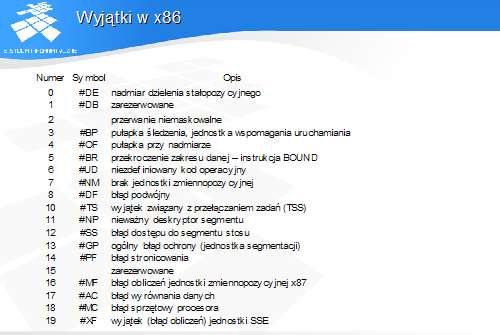

Wyjątki w x86

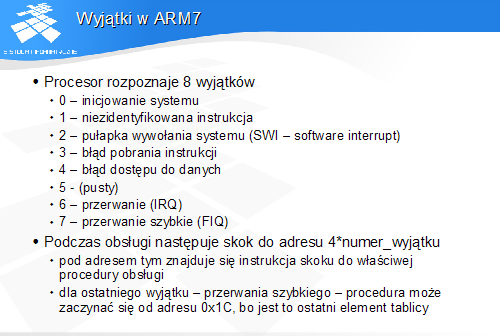

Wyjątki w ARM7

-

Procesor rozpoznaje 8 wyjątków

-

0 - inicjowanie systemu

-

1 - niezidentyfikowana instrukcja

-

2 - pułapka wywołania systemu (SWI - software interrupt)

-

3 - błąd pobrania instrukcji

-

4 - błąd dostępu do danych

-

5 - (pusty)

-

6 - przerwanie (IRQ)

-

7 - przerwanie szybkie (FIQ)

-

Podczas obsługi następuje skok do adresu 4*numer_wyjątku

-

pod adresem tym znajduje się instrukcja skoku do właściwej procedury obsługi

-

dla ostatniego wyjątku - przerwania szybkiego - procedura może zaczynać się od adresu 0x1C, bo jest to ostatni element tablicy

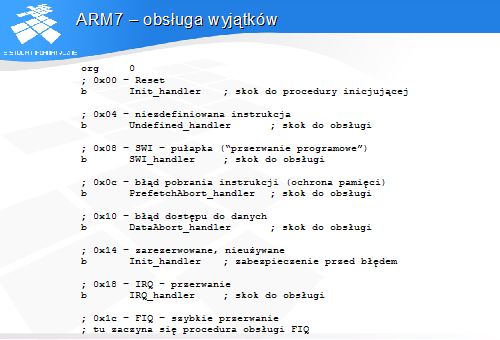

ARM7 - obsługa wyjątków

Powrót z obsługi wyjątku

-

Nie z każdej obsługi wyjątku powrót jest możliwy

-

błąd ochrony może wymagać zamknięcia programu

-

Powrót polega na odtworzeniu informacji zapamiętanych podczas obsługi (co najmniej PC i rejestr stanu)

-

służy do tego specjalna instrukcja powrotu z obsługi wyjątku

-

instrukcja ta jest dozwolona wyłącznie w trybie systemowym, w przeciwnym razie użytkownik mógłby załadować nową wartość rejestru stanu i zmienić poziom zaufania na systemowy

-

W praktyce systemów operacyjnych obsługa wyjątku często kończy się przełączeniem procesu

-

„powrót" z wyjątku następuje do innego strumienia instrukcji, niż strumień przerwany przez wyjątek

-

wykorzystywany mechanizm jest identyczny jak przy powrocie do przerwanego strumienia instrukcji

Asynchroniczne przerwanie programowe

-

Mechanizm implementowany w niektórych procesorach

-

pożyteczny w systemach czasu rzeczywistego

-

Umożliwia zgłoszenie asynchronicznego, maskowalnego przerwania przez sam procesor

-

Przerwanie zostaje obsłużone, gdy poziom wrażliwości procesora na przerwania osiągnie odpowiednią wartość

-

Zwykle używa się tego mechanizmu do zgłoszenia przerwania o niższym priorytecie z procedury obsługi przerwania o wyższym priorytecie

-

cel: kontynuacja akcji wynikających z przerwania przy zachowaniu możliwości reakcji na przerwania o niższych priorytetach

-

można w ten sposób uniknąć inwersji priorytetów, czyli sytuacji, gdy procesor wykonuje czynność o niskim priorytecie jednocześnie nie obsługując przerwania o wyższym priorytecie

Błąd podwójny

-

Podczas obsługi sytuacji wyjątkowych procesory CISC wykonują serię odwołań do pamięci (składowanie kontekstu, ładowanie nowego kontekstu) nie wynikających z wykonania instrukcji

-

Podczas tych odwołań procesor nie ma ważnej wartości licznika instrukcji

-

Odwołania te mogą spowodować błąd związany z zarządzaniem pamięcią

Inicjowanie działania procesora - Reset

-

W wielu procesorach inicjowanie działania jest traktowane jako wyjątek o najwyższym priorytecie

-

Powoduje natychmiastowe przekazanie sterowania pod ustalony adres

-

Nie wymaga składowania kontekstu

Priorytety sytuacji wyjątkowych

-

Priorytet określa pilność obsługi danego wyjątku

-

Dwa aspekty priorytetów odpowiadają dwóm pojęciom obsługi

-

na poziomie procesora

-

na poziomie systemu operacyjnego

-

Priorytety na poziomie systemu - wynikają z pilności zdarzenia

-

przerwania - krytyczne czasowo

-

pułapki (wywołanie systemu) - decyduje o wydajności aplikacji

-

błędy- usunięcie programu, pamięć wirtualna

-

Priorytety na poziomie procesora - wynikają z logicznej sekwencji czynności w procesorze

-

błędy - w razie błędu nie można zakończyć wykonania instrukcji

-

pułapki - obsługa stanowi ostatnią fazę wykonania instrukcji

-

przerwania - obsługiwane po zakończeniu wykonania instrukcji