Poza jednostką stałopozycyjną, procesory rodziny x86 posiadają jednostkę zmiennopozycyjną x87, wprowadzoną jeszcze w latach 70-tych XX wieku i zbudowaną na jej bazie jednostkę wektorową MMX/3DNow! oraz nowszą jednostkę zmiennopozycyjną i wektorową SSE.

Jednostka x87 powoli wychodzi z użycia, chociaż współczesne procesory są w nią wyposażone dla zachowania zgodności binarnej oprogramowania ze starszymi modelami.

Nowe oprogramowanie korzysta z jednostki SSE, a sama jednostka jest intensywnie rozwijana poprzez rozszerzanie listy instrukcji i obsługę nowych formatów danych. Kolejne wersje jednostki są oznaczane jako SSE2, SSE3, SSSE3 i SSE4.

-

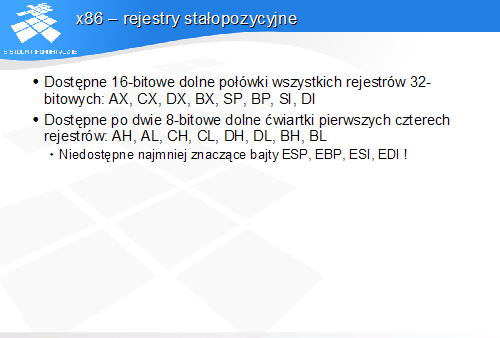

Dostępne 16-bitowe dolne połówki wszystkich rejestrów 32-bitowych: AX, CX, DX, BX, SP, BP, SI, Dl

-

Dostępne po dwie 8-bitowe dolne ćwiartki pierwszych czterech rejestrów AH, AL, CH, CL, DH, DL, BH, BL

-

Niedostępne najmniej znaczące bajty ESP. EBP. ESI. EDI !

Dość nietypową i niewygodną z punktu widzenia konstrukcji kompilatorów cechą x86 jest niedostępność najmniej znaczących bajtów czterech z ośmiu rejestrów. W zamian za to jest możliwy dostęp do kolejnych, „drugich” bajtów czterech pierwszych rejestrów, z czego w praktyce kompilatory nie są w stanie efektywnie skorzystać. Taki model zestawu rejestrów wynika z historii architektury x86 i jej pochodzenia od 8-bitowych procesorów serii 8080.

x86 – adresowanie pamięci w trybie 32-bitowym

-

Adres złożony z trzech składników: [Rb + Ri * S + d]

-

Rb - rejestr bazowy - dowolny

-

Ri - rejestr indeksowy- dowolny oprócz ESP

-

S - skala: 1,2,4, 8

-

d - przemieszczenie lub adres absolutny

-

Każdy z składników opcjonalny, jeden musi wystąpić (jeśli tylko d, to jest to 32-bitowy adres absolutny)

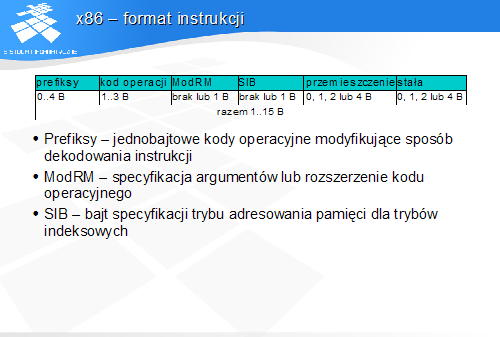

x86 – format instrukcji

-

Prefiksy - jednobajtowe kody operacyjne modyfikujące sposób dekodowania instrukcji

-

ModRM - specyfikacja argumentów lub rozszerzenie kodu operacyjnego

-

SIB - bajt specyfikacji trybu adresowania pamięci dla trybów indeksowych

Szczególną cechą zapisu binarnego instrukcji w x86jest obecność prefiksów – jednobajtowych kodów operacyjnych nie reprezentujących żadnych instrukcji, lecz modyfikujących sposób dekodowania przez procesor następującej po prefiksach instrukcji.

Proste tryby adresowania, w tym rejestrowe pośrednie, są specyfikowane przez bajt ModRM. Tryby indeksowe wymagają następnego bajtu - SIB.

x86 – instrukcje jednostki stałopozycyjnej

-

Pełny opis wszystkich instrukcji jest zawarty w dokumentach: IA-32 Intel® Architecture Software Developer's Manual AMD64 Architecture Programmer's Manual

-

Przedstawimy tylko wybrane instrukcje

-

przesłania

-

podstawowe instrukcje arytmetyczne i logiczne

-

przesunięcia i rotacje bitowe

-

instrukcja LEA

-

mnożenie i dzielenie

-

skoki

-

instrukcje wspomagające implementację języków wysokiego poziomu

Instrukcje przesłań

-

MOV - przesłanie

-

XCHG - wymiana (przesłanie dwukierunkowe)

-

MOVSX - przesłanie danej z rozszerzeniem bitem znaku

-

np. MOVSX EAX, BL-dana 8-bitowa z BL jest rozszerzana do 32 bitów w EAX

-

MOVZX - przesłanie z rozszerzeniem zerami

-

np. MOVZX EAX, AL - dana 8-bitowa z AL zostaje rozszerzona zerami do 32 bitów w EAX

Instrukcje arytmetyczne i logiczne

-

Jednoargumentowe

-

INC, DEC - inkrementacja. dekrementacja

-

NOT, NEG - negacja bitów, zmiana znaku

-

Dwuargumentowe

-

ADD, ADC - dodawanie zwykłe i z przeniesieniem wchodzącym

-

SUB, SBB- odejmowanie zwykłe i z pożyczką wchodzącą

-

CMP - porównanie - odejmowanie bez zapisu wyniku (tylko ustawienie znaczników

-

AND, OR, XOR - iloczyn, suma i różnica symetryczna (bitowe)

-

TEST - iloczyn logiczny bez zapisu wyniku, tylko ustawienie znaczników (podobnie do CMP)

Instrukcje przesunięć i rotacji

-

liczba pozycji przesunięcia zapisana jako stała w instrukcji lub zmienna - w rejestrze CL (brak ortogonalności)

-

SHL, SHR- przesunięcie w lewo/prawo z dopełnieniem zerami

-

SAR - przesunięcie „arytmetyczne" w prawo, z kopiowaniem bitu znaku

-

służy do realizacji dzielenia liczb ze znakiem przez potęgi liczby 2

-

ROL, ROR - rotacja w lewo/prawo

-

RCL, RCR - rotacja w lewo/prawo poprzez bit przeniesienia

-

może służyć do realizacji przesunięć bardzo długich danych o jeden bit

-

SHLD, SHRD- przesunięcie dwóch słów w lewo/prawo z zapisem bardziej/mniej znaczącego słowa wyniku

-

pełne przesunięcie wymaga sekwencji SHLD. SHL lub SHRD. SHR

Instrukcje LEA

-

Load Effective Address - ładuj adres efektywny

-

Zapis jak dla instrukcji MOV z argumentem docelowym w rejestrze i źródłowym w pamięci

-

Ładuje ADRES do rejestru, nie wykonuje przesłania danych

-

Traktowana jak instrukcja przesłania - nie ustawia znaczników

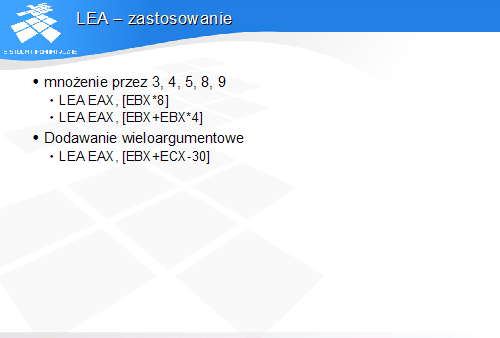

LEA – zastosowanie

-

mnożenie przez 3, 4, 5, 8, 9

-

LEA EAX, [EBX*8]

-

LEA EAX, [EBX+EBX*4]

-

Dodawanie wieloargumentowe

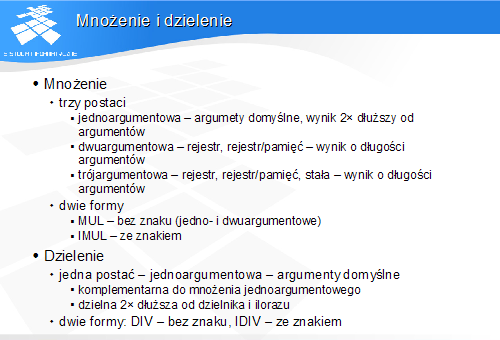

Mnożenie i dzielenie

-

Mnożenie

-

trzy postaci

-

jednoargumentowa - argumety domyślne, wynik 2x dłuższy od argumentów

-

dwuargurnentowa - rejestr, rejestr/pamięć – wynik o długości argumentów

-

trój argumentowa - rejestr, rejestr/pamięć, stała – wynik o długości argumentów

-

dwie formy

-

MUL - bez znaku (jedno- i dwu argumentowe)

-

IMUL-ze znakiem

-

Dzielenie

-

jedna postać - jednoargumentowa - argumenty domyślne

-

komplementarna do mnożenia jednoargumentowego

-

dzielna 2x dłuższa od dzielnika i ilorazu

-

dwie formy DIV - bez znaku. IDlV - ze znakiem

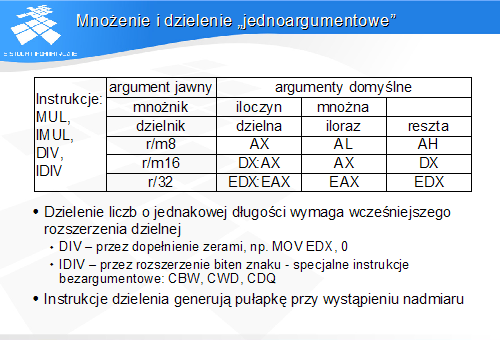

Mnożenie i dzielenie "jednoargumentowe"

-

Dzielenie liczb o jednakowej długości wymaga wcześniejszego rozszerzenia dzielnej

-

DIV - przez dopełnienie zerami, np. MOVEDX, 0

-

IDIV - przez rozszerzenie biten znaku - specjalne instrukcje bezargumentowe: CBW, CWD, CDQ

-

Instrukcje dzielenia generują pułapkę przy wystąpieniu nadmiaru

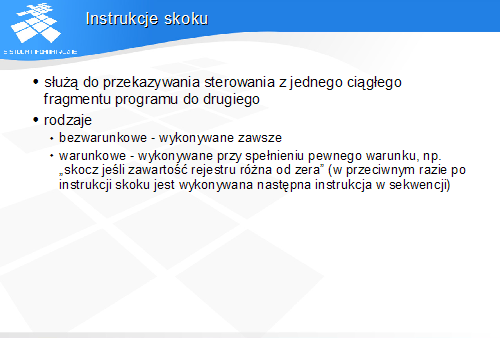

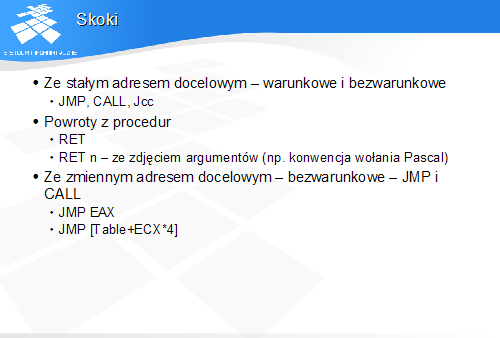

Instrukcje skoku

-

służą do przekazywania sterowania z jednego ciągłego fragmentu programu do drugiego

-

rodzaje

-

bezwarunkowe - wykonywane zawsze

-

warunkowe - wykonywane przy spełnieniu pewnego warunku, np. "skocz jeśli zawartość rejestru różna od zera" (w przeciwnym razie po instrukcji skoku jest wykonywana następna instrukcja w sekwencji)

Skoki

-

Ze stałym adresem docelowym - warunkowe i bezwarunkowe

-

Powroty z procedur

-

RET

-

RET n - ze zdjęciem argumentów (np. konwencja wołania Pascal)

-

Ze zmiennym adresem docelowym - bezwarunkowe - JMP i CALL

-

JMP EAX

-

JMP [Table+ECX*4]

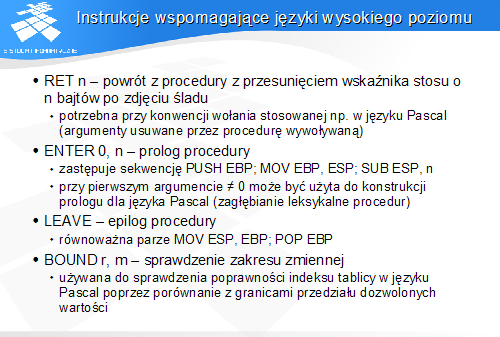

Instrukcje wspomagające języki wysokiego poziomu

-

RET n - powrót z procedury z przesunięciem wskaźnika stosu o n bajtów po zdjęciu śladu

-

potrzebna przy konwencji wołania stosowanej np w języku Pascal (argumenty usuwane przez procedurę wywoływaną)

-

ENTER 0, n - prolog procedury

-

zastępuje sekwencję PUSH EBP: MOV EBP. ESP: SUB ESP, n

-

przy pierwszym argumencie ≠ 0 może być użyta do konstrukcji prologu dla języka Pascal (zagłębianie leksykalne procedur)

-

LEAVE - epilog procedury

-

równoważna parze MOV ESP. EBP: POP EBP

-

BOUND r, m - sprawdzenie zakresu zmiennej

-

używana do sprawdzenia poprawności indeksu tablicy w języku Pascal poprzez porównanie z granicami przedziału dozwolonych wartości

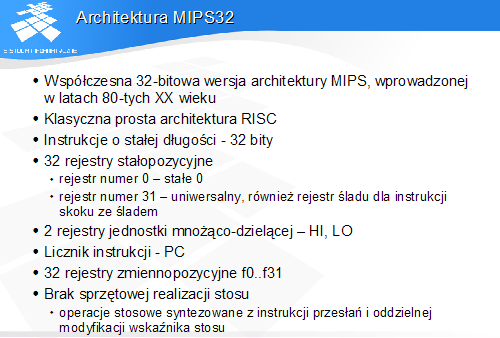

Architektura MIPS32

-

Współczesna 32-bitowa wersja architektury MIPS, wprowadzonej w latach 80-tych XX wieku

-

Klasyczna prosta architektura RISC

-

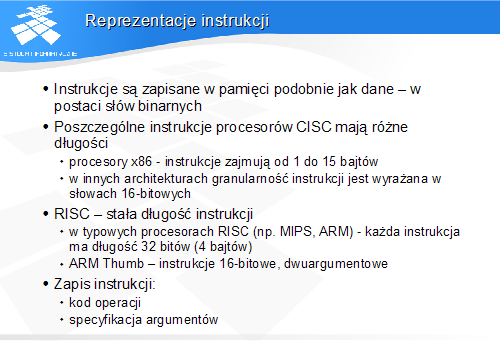

Instrukcje o stałej długości - 32 bity

-

32 rejestry stałopozycyjne

-

rejestr numer 0 - stałe 0

-

rejestr numer 31 - uniwersalny, również rejestr śladu dla instrukcji skoku ze śladem

-

2 rejestry jednostki mnożąco-dzielącej - HI, LO

-

Licznik instrukcji - PC

-

32 rejestry zmiennopozycyjne f0..f31

-

Brak sprzętowej realizacji stosu

-

operacje stosowe syntezowane z instrukcji przesłań i oddzielnej modyfikacji wskaźnika stosu

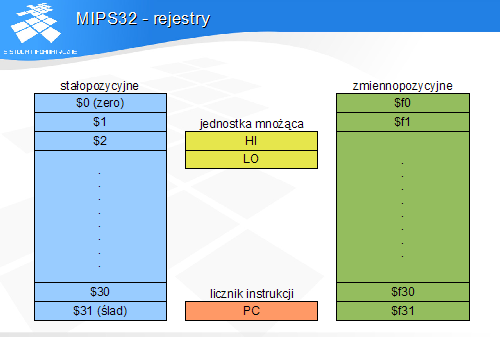

MIPS32 - rejestry

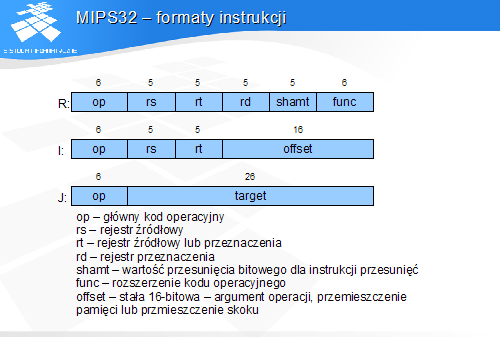

MIPS32 - formaty instrukcji

MIPS32 - instrukcje

-

Format R

-

instrukcje arytmetyczne i logiczne z argumentami w rejestrach

-

skok i skok ze śladem z adresem w rejestrze

-

Format I

-

instrukcje arytmetyczne i logiczne z argumentem natychmiastowym

-

instrukcje wymiany z pamięcią

-

skoki warunkowe (zasięg do 128 KB)

-

Format J

-

skok i skok ze śladem z długim adresem natychmiastowym

16-bitowa stała w formacie I służy, w zależności od instrukcji, jako argument natychmiastowy, przemieszczenie adresu danej w pamięci lub przemieszczenie skoku. Ponieważ instrukcje są zapisane w postaci słów 32-bitowych wyrównanych naturalnie, adres instrukcji jest zawsze podzielny przez 4. Przemieszczenie skoku jest traktowane jako przemieszczenie słowowe – jest ono przesuwane w lewo o dwa bity, co umożliwia uzyskanie zasięgu skoków w zakresie od -128 do +128 KB.

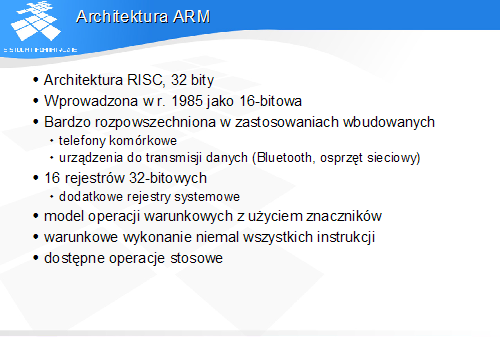

Architektura ARM

-

Architektura RISC, 32 bity

-

Wprowadzona wr. 1985 jako 16-bitowa

-

Bardzo rozpowszechniona w zastosowaniach wbudowanych

-

telefony komórkowe

-

urządzenia do transmisji danych (Bluetooth. osprzęt sieciowy)

-

16 rejestrów 32-bitowych

-

dodatkowe rejestry systemowe

-

model operacji warunkowych z użyciem znaczników

-

warunkowe wykonanie niemal wszystkich instrukcji

-

dostępne operacje stosowe

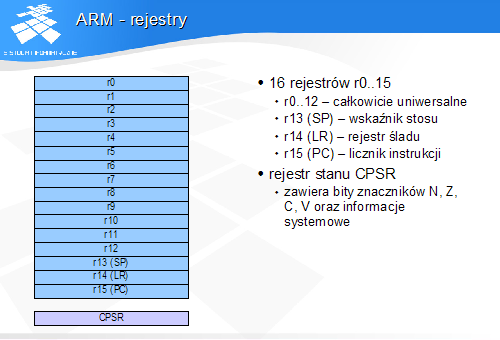

ARM - rejestry

-

16 rejestrów r0..15

-

r0. 12 - całkowicie uniwersalne

-

r 13 (SP) - wskaźnik stosu

-

r14 (LR) - rejestr śladu

-

r 15 (PC) - licznik instrukcji

-

rejestr stanu CPSR

-

zawiera bity znaczników N. Z. C, V oraz informacje systemowe

ARM - charakterystyka instrukcji

-

Pierwotnie instrukcje 32-bitowe

-

trójargumentowe

-

większość instrukcji warunkowa - instrukcje zawierają specyfikacje warunku wykonania

-

Współczesne procesory ARM mają drugi, alternatywny zestaw instrukcji - Thumb

-

instrukcje 16-bitowe. dwuargumentowe

-

ograniczony dostęp do części rejestrów

-

instrukcje warunkowe - tylko skoki