-

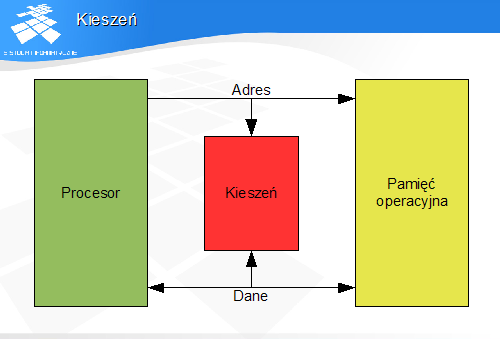

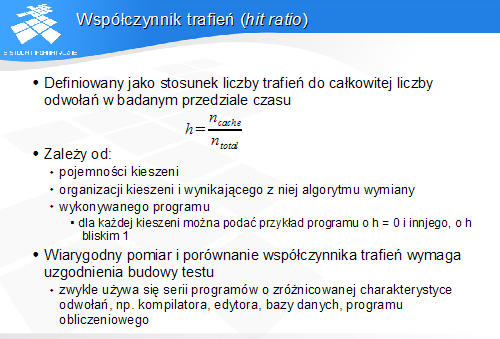

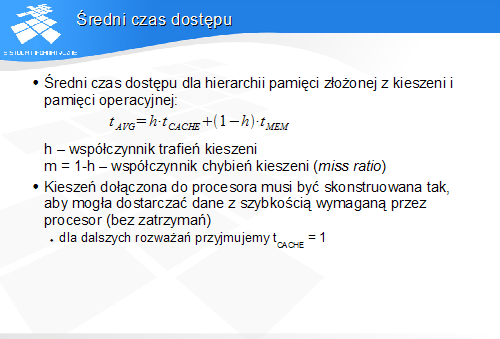

Średni czas dostępu dla hierarchii pamięci złożonej z kieszeni i pamięci operacyjnej:

h - współczynnik trafień kieszeni

m = 1-h - współczynnik chybień kieszeni (miss ratio)

-

Kieszeń dołączona do procesora musi być skonstruowana tak, aby mogła dostarczać dane z szybkością wymaganą przez procesor (bez zatrzymań)

-

dla dalszych rozważań przyjmujemy tCACHE = 1

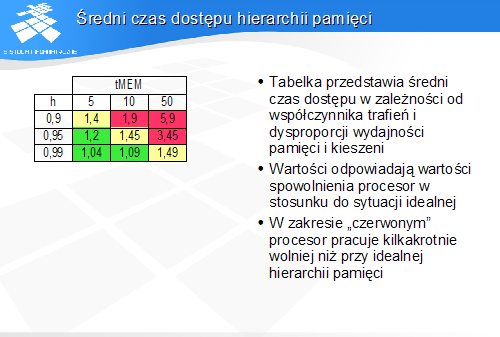

Średni czas dostępu hierarchii pamięci

-

Tabelka przedstawia średni czas dostępu w zależności od współczynnika trafień i dysproporcji wydajności pamięci i kieszeni

-

Wartości odpowiadają wartości spowolnienia procesor w stosunku do sytuacji idealnej

-

W zakresie „czerwonym" procesor pracuje kilkakrotnie wolniej niż przy idealnej hierarchii pamięci

Wydajność kieszeni - wnioski

-

Intuicyjnie „wysoki" współczynnik trafień nie zapewnia zbalansowania wydajności procesora i hierarchii pamięci

-

istotny jest nie tyle współczynnik trafień, co dysproporcja pomiędzy wydajnością kieszeni i pamięci

-

We współczesnych komputerach czas dostępu pamięci może być ponad 100 razy dłuższy od czasu cyklu procesora

-

z tabelki wynika, że nawet bardzo wysoki współczynnik trafień nie umożliwi wyrównania wydajności

-

Pojedyncza kieszeń może skutecznie zniwelować różnicę wydajności nie przekraczającą jednego rzędu dziesiętnego

-

Poprawa średniego czasu dostępu wymaga poprawy czasu dostępu poza kieszenią - można to uzyskać zastępując pamięć operacyjną kolejnym kieszeni i pamięci

-

w ten sposób powstaje wielopoziomowy system kieszeni

Kieszenie wielopoziomowe

-

Wymóg nadążania kieszeni pierwszego poziomu (L1) ogranicza jej pojemność i asocjacyjność

-

im większa kieszeń - tym wolniejsza

-

im wyższa asocjacyjność - tym dłuższy czas dostępu

-

Kieszeń drugiego poziomu (L2) może być wolniejsza (np. 5 razy) - dzięki temu:

-

może mieć wyższą asocjacyjność

-

może być znacząco większa

-

Jeśli kieszeń L2 nie zapewnia odpowiednio krótkiego średniego czasu dostępu, w strukturze komputera umieszcza się kieszeń L3, większą i wolniejszą od L2

Kieszeń a zapis danych

-

W dotychczasowych rozważaniach rozpatrywaliśmy wyłącznie odczyt danych lub instrukcji z pamięci

-

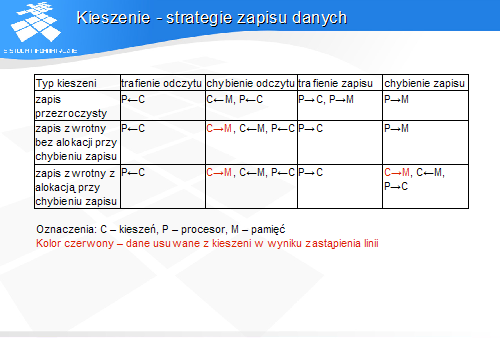

Możliwe zachowanie kieszeni przy zapisie:

-

zapis przezroczysty - zapis wykonywany zawsze do pamięci, a w przypadku trafienia - również do kieszeni

-

zapis zwrotny- zapis do pamięci wykonywany tylko wtedy, kiedy jest to niezbędne

-

Warianty zapisu zwrotnego:

-

bez alokacji przy chybieniu zapisu - w razie chybienia zapis zachodzi tylko do pamięci, w razie trafienia - tylko do kieszeni

-

z alokacją przy chybieniu zapisu - zapis jest zawsze wykonywany tylko do kieszeni

-

Przy zapisie zwrotnym usunięcie linii z kieszeni może wymagać zapisu usuwanej linii do pamięci

Kieszenie - strategie zapisu danych

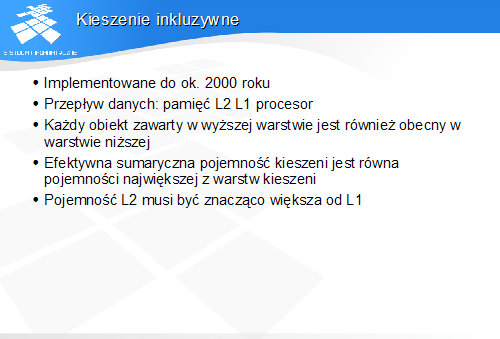

Kieszenie inkluzywne

-

Implementowane do ok. 2000 roku

-

Przepływ danych: pamięć L2 L1 procesor

-

Każdy obiekt zawarty w wyższej warstwie jest również obecny w warstwie niższej

-

Efektywna sumaryczna pojemność kieszeni jest równa pojemności największej z warstw kieszeni

-

Pojemność L2 musi być znacząco większa od L1

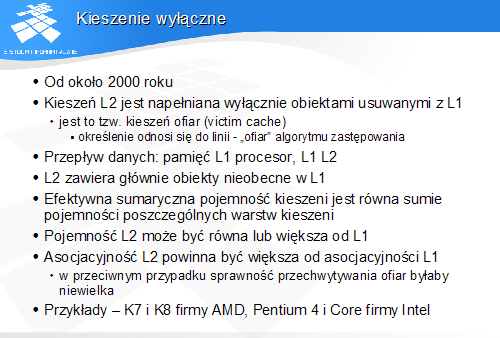

Kieszenie wyłączne

-

Od około 2000 roku

-

Kieszeń L2 jest napełniana wyłącznie obiektami usuwanymi z L1

-

jest to tzw. kieszeń ofiar (victim cache)

-

określenie odnosi się do linii - "ofiar" algorytmu zastępowania

-

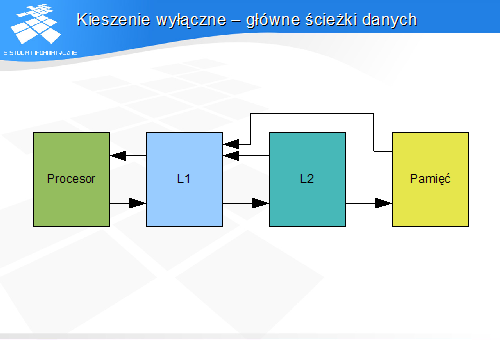

Przepływ danych: pamięć L1 procesor, L1 L2

-

L2 zawiera głównie obiekty nieobecne w L1

-

Efektywna sumaryczna pojemność kieszeni jest równa sumie pojemności poszczególnych warstw kieszeni

-

Pojemność L2 może być równa lub większa od L1

-

Asocjacyjność L2 powinna być większa od asocjacyjności L1

-

w przeciwnym przypadku sprawność przechwytywania ofiar byłaby niewielka

-

Przykłady - K7 i K8 firmy AMD, Pentium 4 i Core firmy I ntel

Kieszenie wyłączne - główne ścieżki danych

Spójność hierarchii pamięci

-

Hierarchię pamięci musi cechować spójność:

-

każdy dostęp do danego adresu musi zwrócić tę samą wartość danej, niezależnie od warstwy, w której jest fizycznie realizowany

-

Problem z utrzymaniem spójności powstaje, gdy istnieje więcej niż jedna ścieżka dostępu do hierarchii pamięci, np.:

-

procesor o architekturze Harvard-Princeton z odzielnymi kieszeniami L1 kodu i danych

-

dwa procesory z oddzielnymi kieszeniami L1 i wspólną dalszą warstwą hierarchii pamięci

-

procesor z kieszenią i sterownik wejścia-wyjścia, wykonujący bezpośrednie dostępy do pamięci z pominięciem kieszeni

-

Spójność nie wymaga utrzymywania identycznej zawartości we wszystkich warstwach, a jedynie zagwarantowania, że każdy dostęp będzie dotyczył aktualnej wartości danej

Metody utrzymywania spójności

-

Unieważnianie całej kieszeni przy wykryciu odwołania zewnętrznego

-

stosowane dawniej przy b. małych kieszeniach

-

Selektywne unieważnianie linii potencjalnie zawierających adres odwołania zewnętrznego

-

stosowane do ok. 1990 roku przy kieszeniach o pojemnościach do kilku KB

-

Programowe unieważnianie całej kieszeni

-

dostępne dla systemu operacyjnego, ograniczone zastosowanie z powodu spadku wydajności

-

Selektywna zmiana stanu linii po stwierdzeniu zgodności adresu, przesłania między kieszeniami

-

metody używane współcześnie, wydajne, ale złożone w realizacji

-

wymagają realizacji złożonych protokołów utrzymania spójności

Protokoły utrzymania spójności

-

Automat zrealizowany oddzielnie dla każdej linii

-

Stany linii:

-

M - modified - linia ważna, jedyna aktualna kopia we własnej kieszeni, zawartość pamięci nieaktualna

-

E - exclusive - linia ważna, jedyna kopia we własnej kieszeni, identyczna z zawartością pamięci

-

I - invalid - linia nieważna

-

S - shared - linia ważna, jednakowa kopia u wszystkich, identyczna z zawartością pamięci

-

O - owned - linia ważna, jednakowa kopia u wszystkich, u pozostałych stan S. zawartość pamięci nieaktualna

-

Protokoły - nazwy pochodzą od zbioru obsługiwanych stanów

-

Im więcej stanów, tym mniej zbędnych unieważnień